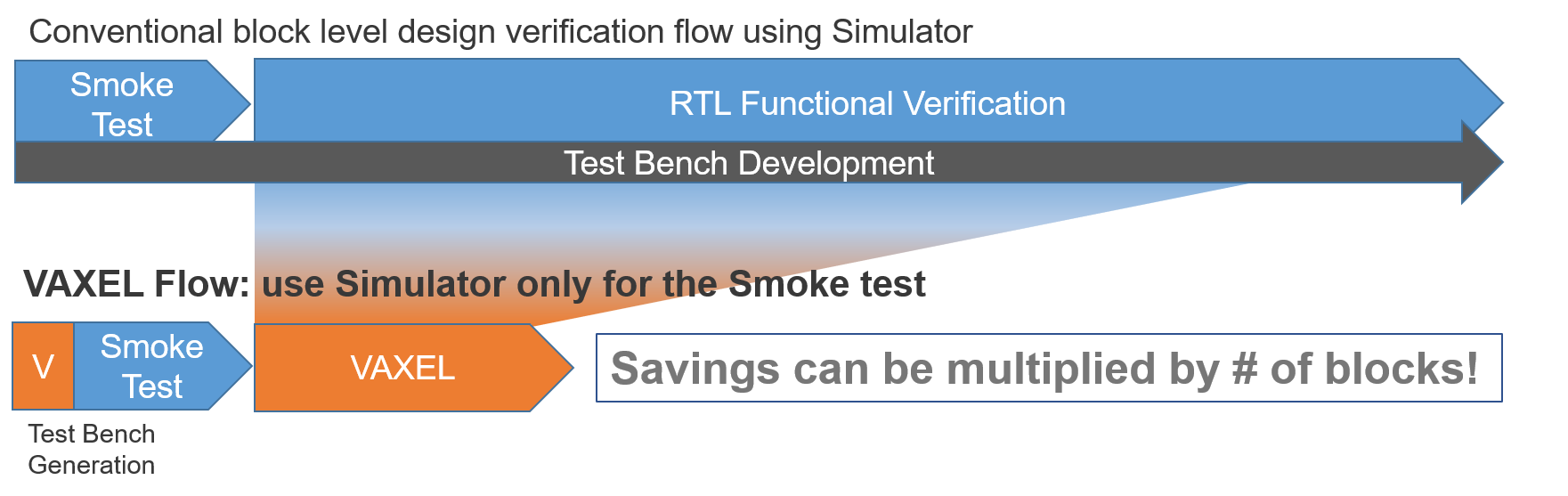

VAXEL is ALL About Saving Time

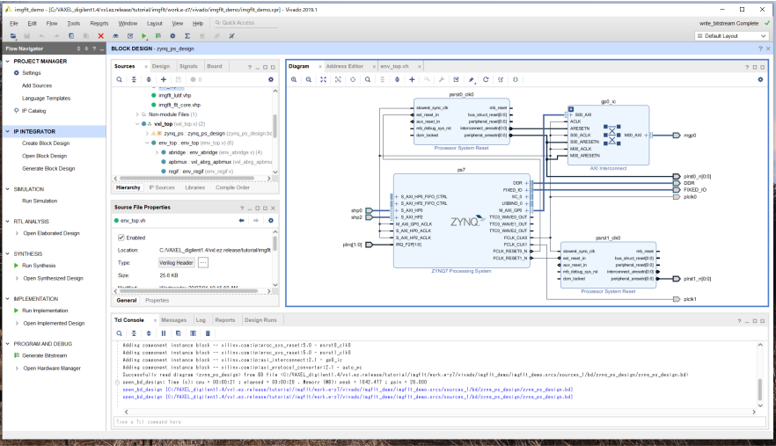

RTL design verification acceleration solution using FPGA needing little FPGA expertise.

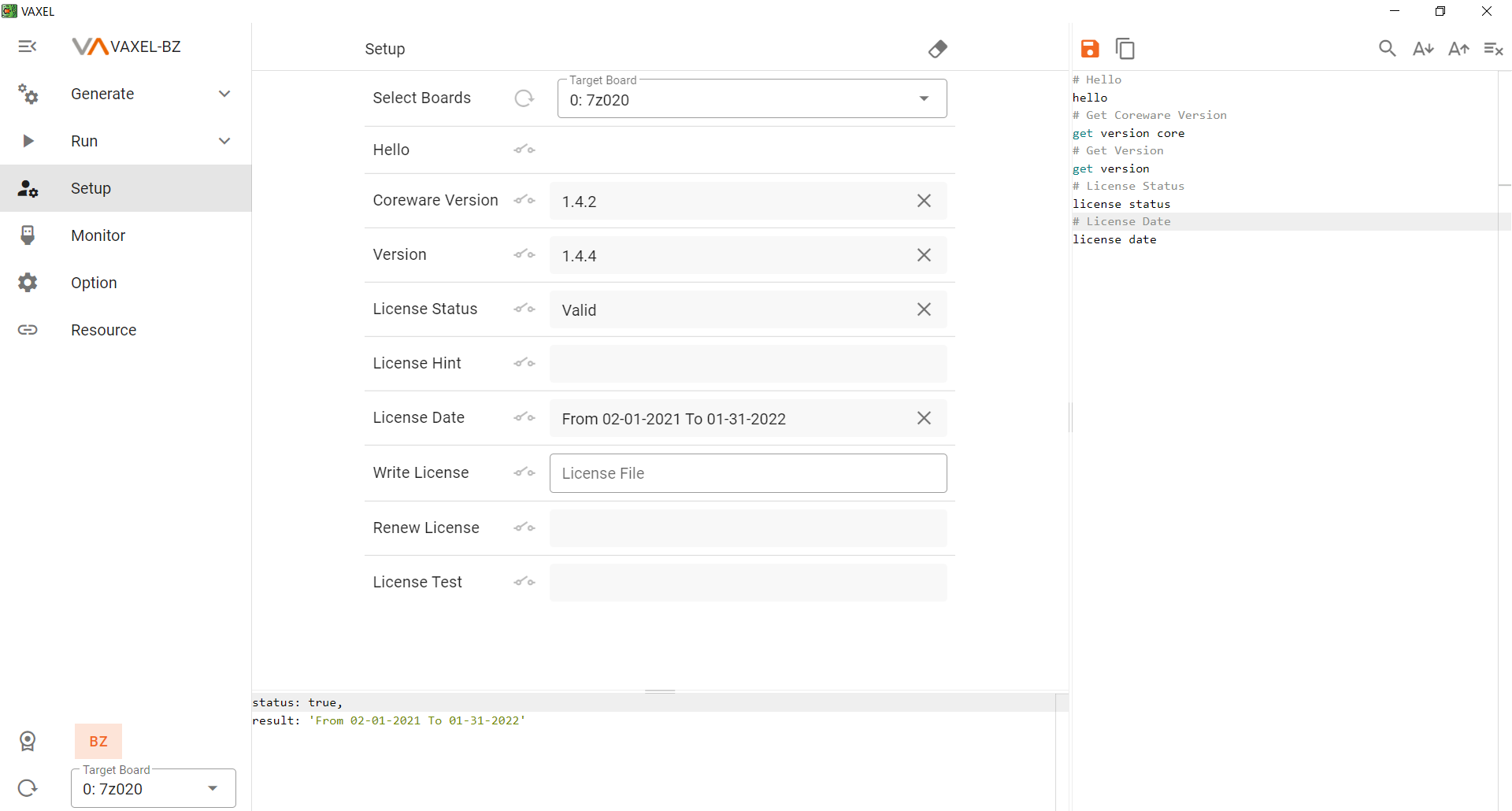

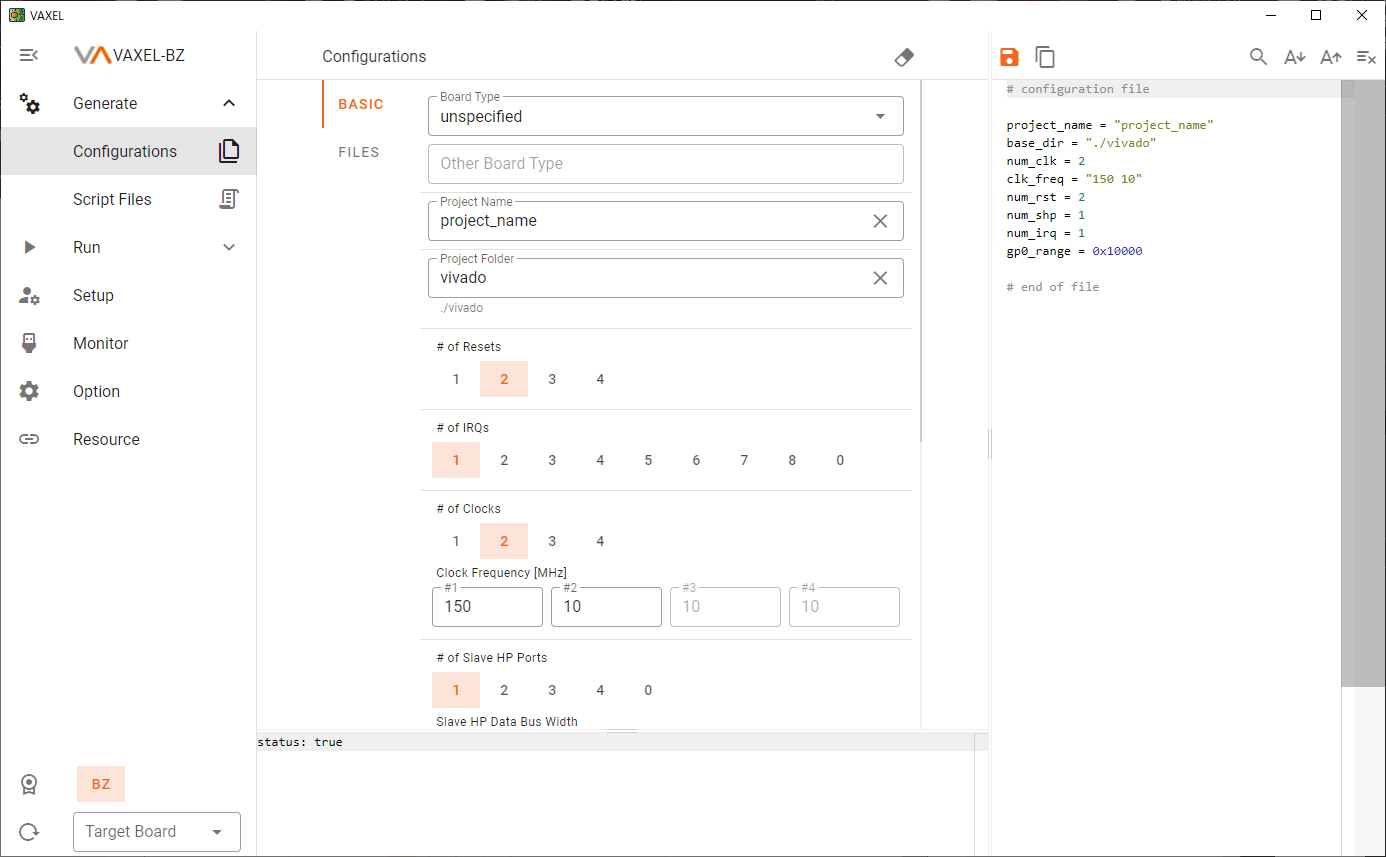

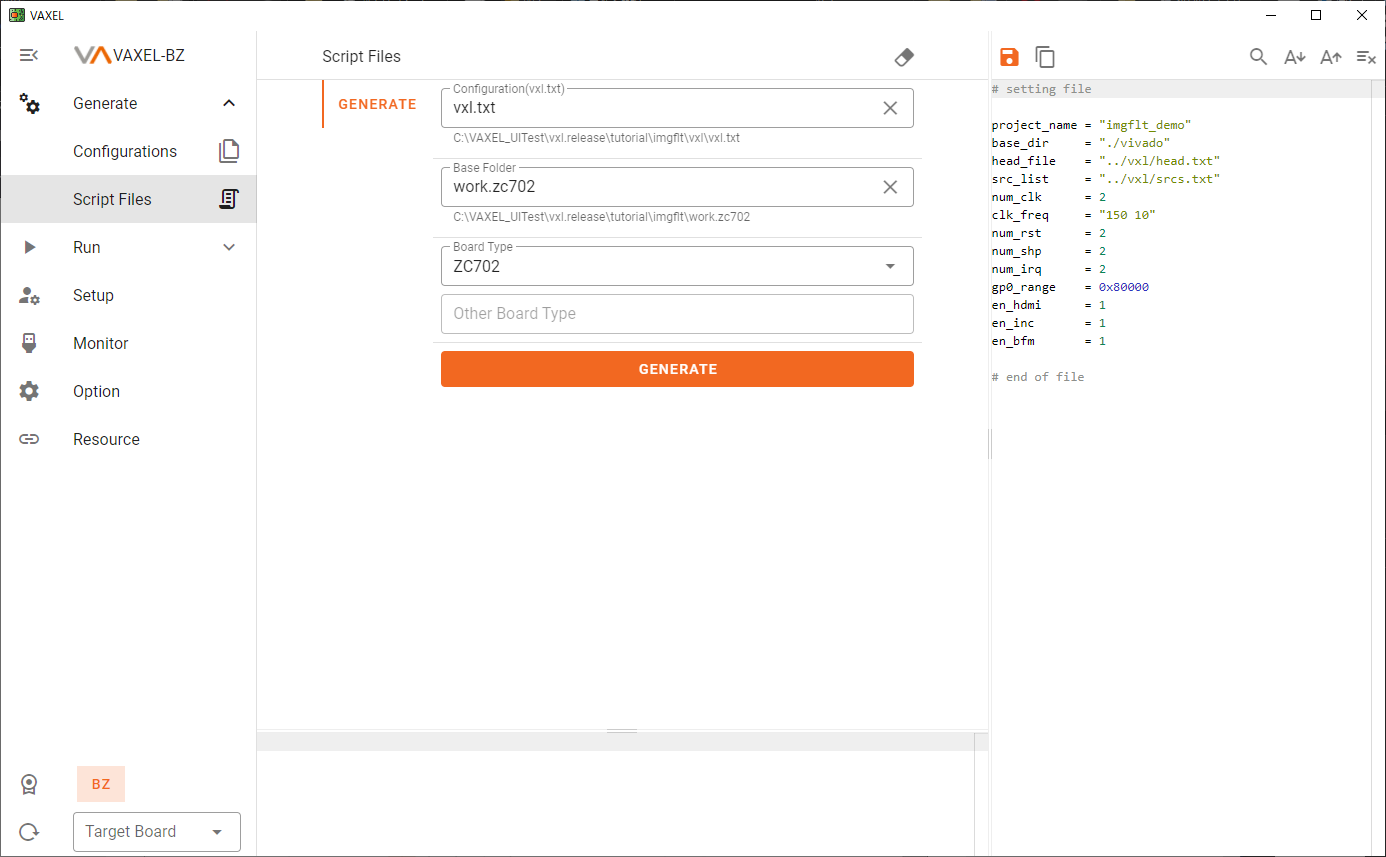

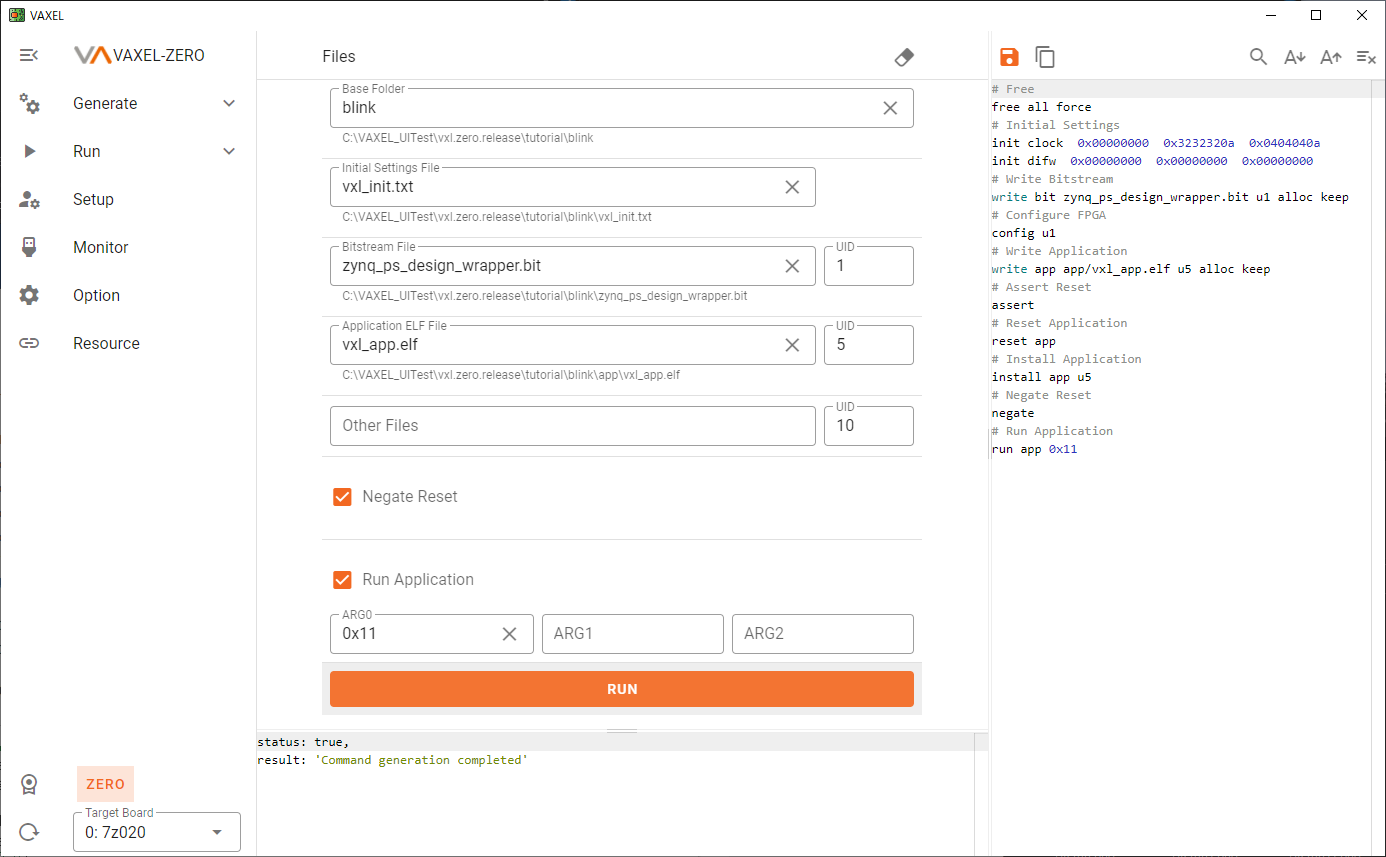

User friendly VAXEL-GUI

Comparison table with emulator and prototyping

Significant time-saving by improving your RTL design quality early in the project

Executing tests at a speed of hardware (FPGA)

No more FPGA expertise needed

Taking advantage of enhanced assertion and waveform tools

Choosing from over 60 pre-validated verification IP blocks

Reaching target coverage fast by our patent-pending intelligent test generator tool

Getting software engineers (Python and C) involved in the RTL verification